Step into the realm of technological achievements with an enthralling journey into the heart of modern electronic engineering. In this article, we delve into the realm of innovative microprocessors, unraveling the capabilities of an extraordinary piece of hardware.

Introducing a groundbreaking marvel that revolutionizes the landscape of digital design, we present an in-depth exploration of the unparalleled potential of advanced programmable logic devices. With an insatiable hunger for efficiency, flexibility, and performance, this remarkable component has emerged as a game-changer in the realm of electrical engineering.

Unleashing the potential of limitless creative possibilities, this article takes you on a captivating voyage through the intricacies of this advanced digital companion. By harmoniously combining logical elements and reconfigurable designs, this programmable marvel empowers engineers and enthusiasts alike, enabling them to shape the future of technological progress.

Overview of Max v CPLD Documentation

Within this section, we will provide a comprehensive introduction to the documentation accompanying the Max v CPLD. This encompasses a collection of essential resources aiming to enhance your understanding and familiarity with this cutting-edge device.

Through a series of guidelines, instructions, and technical explanations, this documentation grants you exclusive access to a wealth of information pertaining to the Max v CPLD. By studying these materials, you will gain insights into the vast capabilities and intricacies that this programmable logic device offers.

Our objective is to empower users with the knowledge needed to effectively harness the potential of the Max v CPLD. The documentation provided here serves as a roadmap, guiding you through the various aspects, capabilities, and applications of this sophisticated device.

To facilitate your journey, we have carefully curated this collection of resources to provide a holistic and comprehensive understanding of the Max v CPLD. Through concise explanations, illustrations, and examples, we aim to simplify complex concepts, ensuring that users of all skill levels can successfully navigate this cutting-edge technology.

By delving into this documentation, readers will be equipped with the know-how required to leverage the Max v CPLD to its fullest extent. With each section of the documentation providing unique insights and guidance, you will amass a solid foundation of expertise, enabling you to optimize the performance and efficiency of your designs.

So dive into the world of Max v CPLD documentation and embark on a journey of discovery. Unleash your creativity, push the boundaries of what is possible, and unlock the full potential of this remarkable programmable logic device.

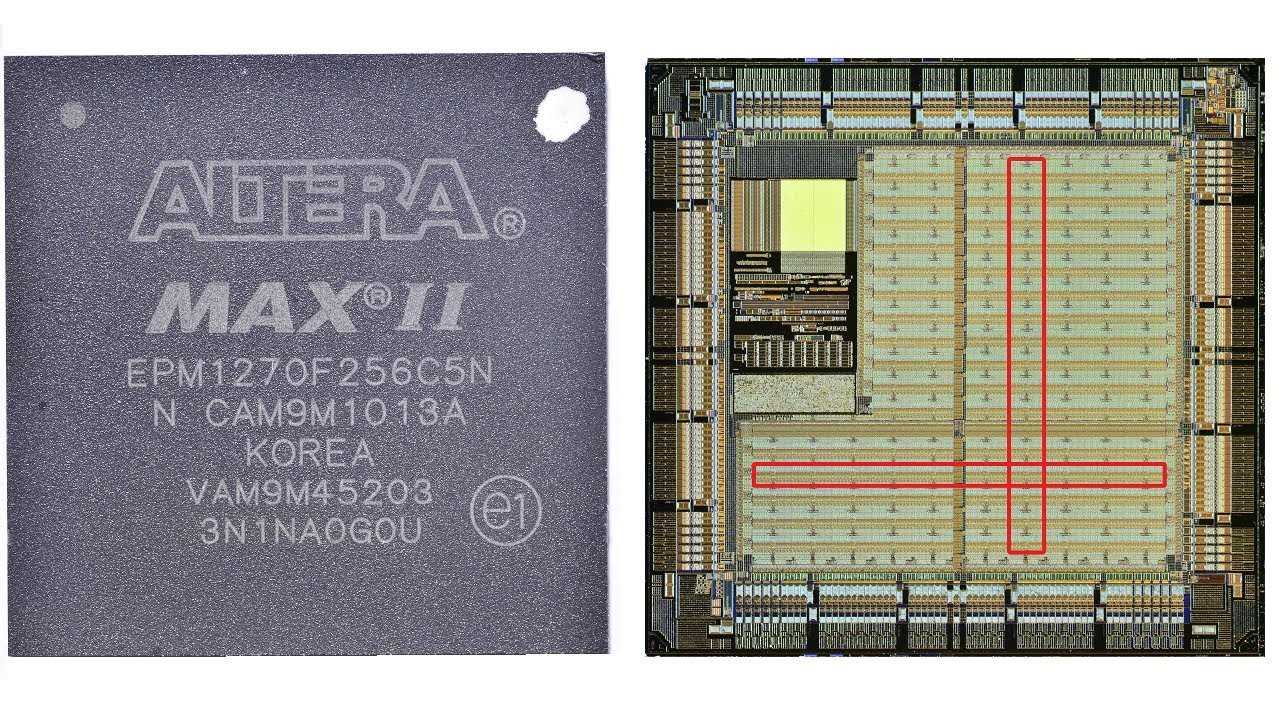

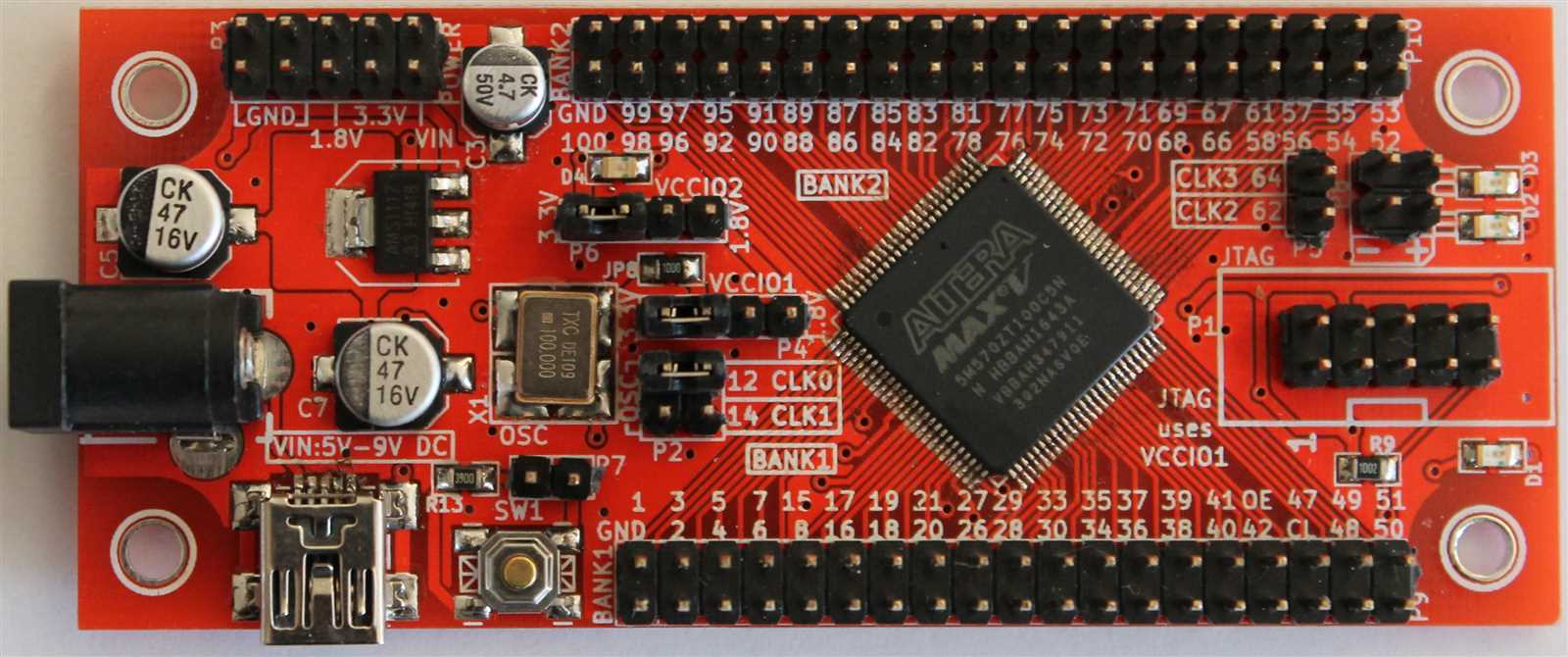

Understanding the Architecture and Pin Configuration

In this section, we will explore the underlying structure and pin arrangement of the device, shedding light on its internal workings. By gaining a deeper understanding of the architecture, you will be better equipped to utilize this technology effectively.

First and foremost, it is crucial to comprehend the intricate design of the device’s architecture. By delving into its inner workings, we can grasp the intricate network of interconnected components that enable its functionality. This intricate architecture serves as the foundation for the device’s capabilities, ensuring reliable and efficient operation.

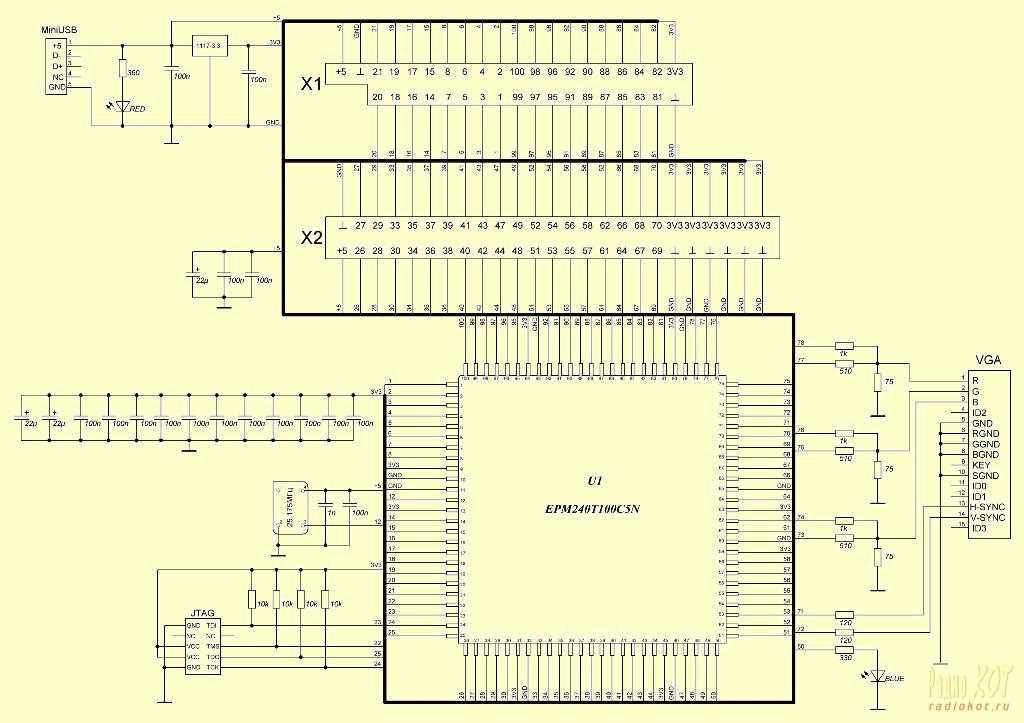

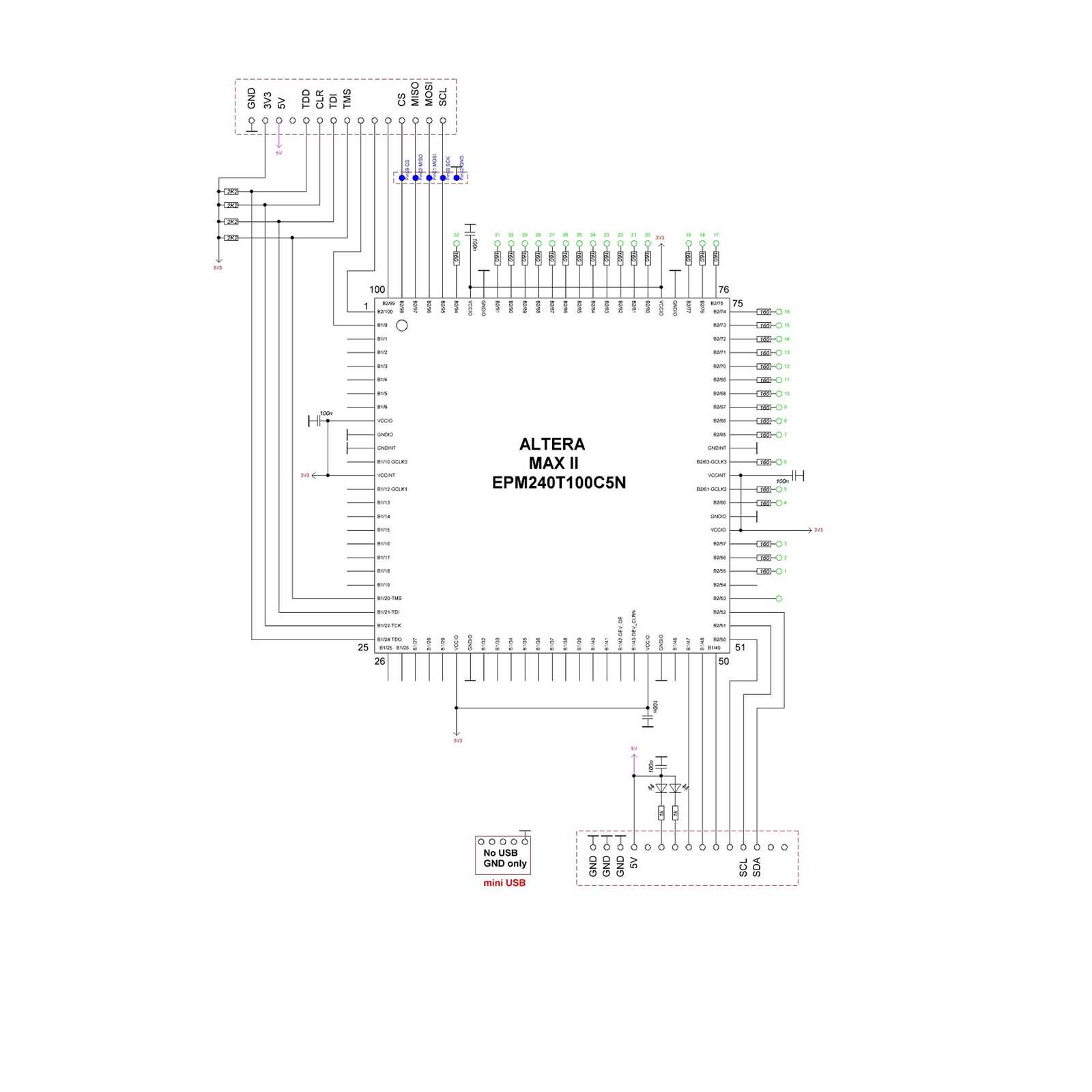

Additionally, a comprehensive exploration of the pin configuration is essential. The pin configuration plays a pivotal role in establishing the device’s connectivity with external components and devices. Understanding how the pins are organized and their designated functions allows for seamless integration into larger systems.

During the discussion, emphasis will be placed on elucidating the relationships between various pins and their corresponding tasks. By examining the pin configuration in detail, you will gain insights into the device’s versatility and adaptability to different applications.

Furthermore, understanding the pin configuration also enables efficient troubleshooting and debugging when issues arise. Being familiar with the interconnections between pins and their purposes allows for targeted identification and resolution of problems, enhancing the overall reliability of the device.

In conclusion, comprehending the architecture and pin configuration of the device lays the groundwork for harnessing its full potential. By delving into the internal structure and connectivity options, you will gain valuable knowledge necessary for exploiting its capabilities effectively within your designs.

Exploring the Functional Blocks and I/O Interfaces

In this section, we will delve into the various functional blocks and input/output (I/O) interfaces of the MAX V CPLD (Complex Programmable Logic Device). By understanding the different components and capabilities of the device, we can gain insights into its potential applications and how it can be effectively utilized in various electronic systems.

Functional Blocks

The MAX V CPLD comprises several functional blocks that enable it to perform a wide range of tasks. One such block is the programmable logic array (PLA), which allows for the implementation of custom logic functions. With the PLA, users can define their own Boolean equations and create tailored logic circuits.

Another essential functional block is the sequential element, which consists of flip-flops and registers. These elements enable the storage and manipulation of data, making it possible to create complex sequential logic circuits. The MAX V CPLD also includes dedicated multiplier blocks that allow for efficient multiplication operations.

Additionally, the device features embedded memory blocks, which provide storage capabilities for data and configuration resources. These memory blocks can be used to store lookup tables, coefficients, or any other data required by the system.

I/O Interfaces

The MAX V CPLD supports a variety of I/O interfaces, making it compatible with diverse external devices and systems. It includes numerous general-purpose I/O pins that can be configured as inputs or outputs depending on the application requirements.

Furthermore, the device offers specialized I/O interfaces, such as high-speed serializers/deserializers (SERDES) and differential signaling interfaces. These interfaces enable the transmission and reception of data at high speeds, making the MAX V CPLD suitable for applications that demand high-performance data communication.

Moreover, the device supports various communication protocols, including serial communication protocols like SPI (Serial Peripheral Interface) and I2C (Inter-Integrated Circuit), as well as parallel interfaces such as LVDS (Low Voltage Differential Signaling) and LVCMOS (Low Voltage Complementary Metal-Oxide-Semiconductor).

By providing such a versatile range of I/O interfaces, the MAX V CPLD offers flexibility in connecting with external devices and systems, expanding its potential applications across different industries and electronic projects.

- Summarizing the key points:

- The MAX V CPLD consists of several functional blocks, including a programmable logic array (PLA), sequential elements, multiplier blocks, and embedded memory.

- It supports various I/O interfaces, including general-purpose I/O pins, high-speed SERDES, differential signaling interfaces, and communication protocols such as SPI, I2C, LVDS, and LVCMOS.