Delving into the intricate network of interconnected components, one often encounters a labyrinth of technical documentation. These resources serve as the backbone of understanding, providing insight into the inner workings of devices and systems. In this realm of knowledge, each document acts as a map, guiding engineers and enthusiasts through the complexities of modern technology.

Within these textual blueprints lie the keys to unlocking the full potential of electronic marvels. They offer not just a glimpse, but a comprehensive view of circuitry, protocols, and functionalities. Such documents, while often overlooked, are indispensable tools for those seeking to unravel the mysteries concealed within integrated circuits and hardware configurations.

Embark on a journey through the pages of technical enlightenment, where terminology serves as signposts, guiding readers toward a deeper comprehension of electronic ecosystems. This exploration goes beyond mere words on paper; it is a quest for understanding, a pursuit of mastery over the intricacies that define our digital landscape.

JTAG Datasheet: Understanding the Basics

In this segment, we delve into the foundational principles underpinning the intricate realm of boundary scan technology. Exploring the core concepts without resorting to specific terminology, we navigate through the fundamental framework that facilitates integrated circuit testing and debugging. Let’s embark on a journey through the rudimentary aspects of this pervasive methodology, unraveling its significance in contemporary electronic engineering.

Exploring the Fundamentals of Boundary Scan Technology

Delving into the core principles of modern electronic testing unveils a realm where connectivity and diagnostics converge to form the backbone of contemporary hardware assessment. Within this domain lies the intricate network of Boundary Scan technology, a sophisticated methodology pivotal in examining the integrity and functionality of integrated circuits.

The Essence of Boundary Scan

At its essence, Boundary Scan epitomizes a paradigm shift in electronic testing, transcending conventional methods to offer unparalleled insight into the inner workings of complex circuitry. By seamlessly integrating testability within the device itself, Boundary Scan redefines the landscape of fault detection and diagnosis, fostering efficiency and accuracy in the realm of hardware validation.

Unraveling the Core Concepts

Peeling back the layers of Boundary Scan technology reveals a tapestry woven with intricate concepts such as scan chains, boundary cells, and test access ports. These foundational elements collectively orchestrate a symphony of connectivity, enabling comprehensive testing and debugging across a spectrum of electronic components.

- Scan Chains: Serving as the backbone of Boundary Scan, scan chains facilitate the serial shift of test data through interconnected boundary cells, enabling exhaustive examination of internal node states.

- Boundary Cells: Embedded within the periphery of integrated circuits, boundary cells act as gatekeepers, facilitating the seamless transfer of test patterns and the observation of internal signals.

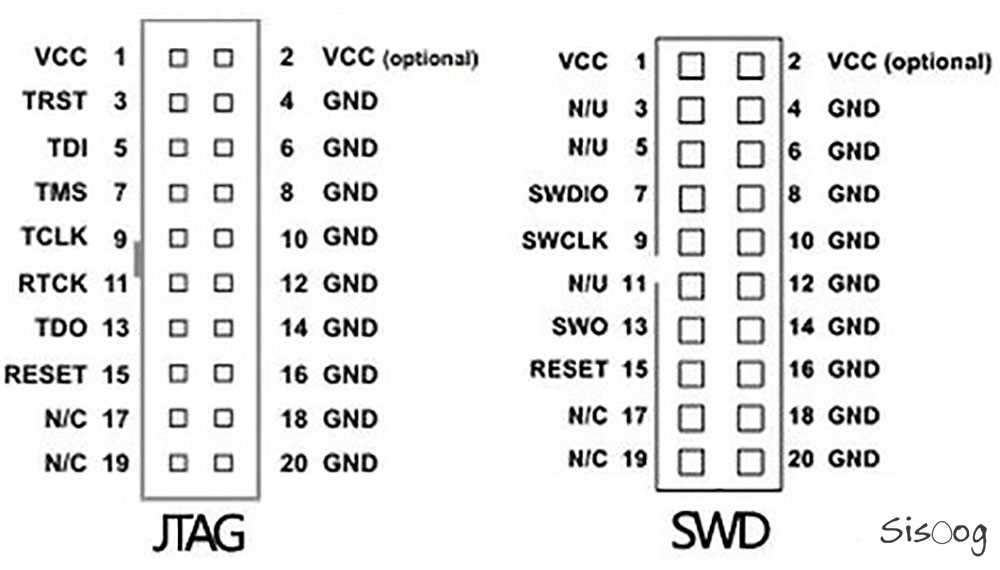

- Test Access Ports (TAPs): Acting as the gateway to device testing, Test Access Ports provide a standardized interface for communication between external test equipment and the internal components of the device under test.

Through a nuanced exploration of these fundamental principles, one can navigate the intricacies of Boundary Scan technology, harnessing its potential to elevate the standards of electronic testing and validation.

Unlocking Advanced Features: Exploring the Potential of Embedded Debugging Interfaces

Delving into the intricacies of contemporary embedded systems unveils a realm where hidden functionalities await discovery. This section embarks on a journey to unravel the latent capabilities of the debug interface, a pivotal component in modern electronics. By meticulously analyzing the technical documentation, a wealth of advanced features and functionalities can be unveiled, elevating the understanding and utilization of embedded systems to new heights.

The Anatomy of Embedded Debugging Interfaces

Before delving into the depths of advanced functionalities, it’s imperative to grasp the fundamental structure and operation of embedded debugging interfaces. These intricate pathways, akin to the neural networks of electronic devices, serve as gateways to the underlying hardware, facilitating communication and control with unparalleled precision. Understanding the nuances of these interfaces lays the foundation for unlocking their hidden potentials.

Unveiling Hidden Capabilities: A Table Analysis

One of the most effective methods for uncovering the concealed functionalities of debugging interfaces is through meticulous examination of technical specifications and registers. In the following table, we present a structured analysis of key parameters and configurations, shedding light on the untapped potential lying dormant within the datasheet.

| Register | Description | Functionality |

|---|---|---|

| DBG_CTRL | Control Register | Enables various debug features |

| DBG_STATUS | Status Register | Indicates current debug status |

| DBG_TRACE_CONFIG | Trace Configuration Register | Configures trace output parameters |

By dissecting and interpreting these registers in conjunction with the provided documentation, a deeper understanding of the debugging interface emerges, paving the way for the exploration and exploitation of advanced features.

Utilizing JTAG Documentation for Enhanced Functionality

Unlocking the full potential of embedded systems requires a comprehensive understanding of their internal mechanisms and interfaces. In the realm of hardware debugging and testing, access to detailed documentation plays a pivotal role in harnessing the capabilities of embedded systems. This section explores the significance of leveraging comprehensive documentation related to the Joint Test Action Group (JTAG) interface for optimizing functionality and performance.

Understanding the Inner Workings: Delving into the intricacies of hardware protocols empowers developers to manipulate system behavior with precision. By delving into the intricacies of hardware protocols, developers gain insights into the inner workings of embedded systems, enabling them to tailor functionalities to specific requirements. Mastery of JTAG documentation unveils the intricate communication pathways within a device, facilitating fine-grained control over its operations.

Enhancing Debugging Capabilities: A detailed understanding of JTAG documentation equips developers with a potent arsenal for debugging embedded systems. By leveraging comprehensive documentation, developers can efficiently identify and rectify hardware-level issues, minimizing development cycles and optimizing time-to-market. Additionally, the ability to interpret JTAG documentation enables the implementation of advanced debugging techniques, fostering robustness and reliability in embedded applications.

Facilitating System Optimization: Harnessing the wealth of information embedded within JTAG documentation empowers developers to optimize system performance and efficiency. By deciphering the intricacies of hardware configurations and communication protocols, developers can fine-tune system parameters to maximize throughput and minimize latency. Moreover, detailed documentation facilitates the identification of potential bottlenecks, paving the way for targeted optimizations and performance enhancements.

Enabling Customization and Innovation: In the ever-evolving landscape of embedded systems, customization and innovation are paramount for staying ahead of the curve. Through a profound understanding of JTAG documentation, developers gain the insights necessary to implement bespoke features and functionalities tailored to specific use cases. By harnessing the flexibility afforded by comprehensive documentation, developers can unleash their creativity, driving innovation and differentiation in their embedded solutions.

Conclusion: The utilization of JTAG documentation serves as a cornerstone for unlocking enhanced functionality and performance in embedded systems. By delving into the intricacies of hardware protocols, developers can elevate their debugging capabilities, optimize system performance, and drive innovation in their embedded applications. Embracing the wealth of information encapsulated within JTAG documentation empowers developers to push the boundaries of what’s possible, ushering in a new era of embedded system design and development.

Optimizing Development: Leveraging JTAG Datasheets

Streamlining the development process requires a deep understanding of the tools and resources available. In the realm of embedded systems, harnessing the full potential of connectivity and debugging interfaces is paramount. This section delves into the strategic utilization of comprehensive technical documentation to enhance efficiency and efficacy in development workflows.

Unlocking Embedded Insights: Embracing the wealth of information embedded within technical documents empowers developers to navigate complexities with precision. By delving into the intricacies of connectivity protocols and system architectures, developers gain invaluable insights into optimizing performance and functionality.

Strategic Navigation: Seamlessly navigating through the labyrinth of technical specifications demands a strategic approach. Leveraging datasheets as navigational aids facilitates swift and informed decision-making, fostering a cohesive development trajectory.

Enhanced Debugging Capabilities: Beyond mere documentation, datasheets serve as blueprints for unlocking advanced debugging capabilities. By deciphering the nuances of signal flows and protocol intricacies, developers can expedite troubleshooting processes and bolster system reliability.

Facilitating Collaborative Development: Harnessing the collective wisdom encapsulated within datasheets fosters collaborative synergy. Through shared understanding and interpretation of technical specifications, development teams can synchronize efforts and accelerate project timelines.