Delve into the intricate world of hardware innovation as we uncover the secrets behind a pivotal component in modern audio technology. Behind the sleek exterior of your favorite gadgets lies a labyrinth of electronic marvels, each carefully crafted to deliver an immersive audio experience. In this exploration, we unravel the mysteries surrounding a cornerstone element, shedding light on its inner workings and unparalleled capabilities.

Embark on a journey through the heart of audio engineering, where every circuit and connection holds the potential to redefine the way we perceive sound. Prepare to be captivated by the fusion of science and artistry as we dissect the essence of audio reproduction, transcending mere function to achieve pure auditory bliss.

Join us as we navigate the intricate landscape of technological advancement, uncovering the nuances of a vital component that powers the melodies of modern life. Through meticulous analysis and expert insight, we unveil the symbiotic relationship between innovation and ingenuity, showcasing the transformative potential of groundbreaking audio solutions.

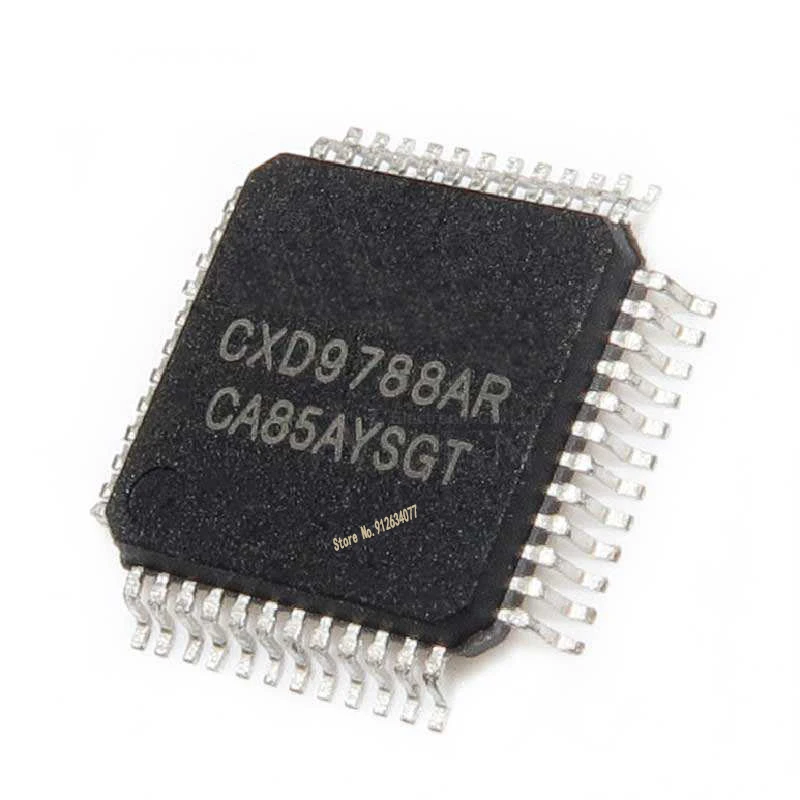

The Basics of Understanding the CX20561 Documentation

In this section, we delve into the fundamental aspects of comprehending the technical documentation related to the CX20561 chipset. By exploring the foundational elements of this documentation, we aim to provide a clear roadmap for navigating and interpreting the essential information encapsulated within.

Fundamental Concepts

- Core Functionality: Explore the primary functionalities encapsulated within the CX20561 documentation, highlighting its pivotal role in various applications.

- Technical Specifications: Gain insights into the detailed technical specifications encompassed within the documentation, elucidating the key parameters and performance metrics.

Interpretation Strategies

- Contextual Analysis: Learn effective strategies for contextual analysis, enabling a deeper understanding of the information presented within the CX20561 documentation.

- Comparative Evaluation: Discover the significance of comparative evaluation techniques in discerning the nuances and distinguishing features of the CX20561 chipset.

By familiarizing oneself with the fundamental concepts and interpretation strategies outlined in this section, readers can embark on a journey towards a comprehensive understanding of the CX20561 documentation, thereby facilitating informed decision-making and efficient utilization of the chipset’s capabilities.

Understanding the Essential Specifications

Delving into the intricacies of a component’s specifications is paramount for grasping its functionality and potential applications. In this section, we aim to dissect the critical specifications of the component in question, shedding light on its performance metrics and capabilities.

Functional Overview

Unveiling the operational framework, we delve into the fundamental principles underlying the component’s functionality. By comprehending its operational mode and core functionalities, users can envision its integration within diverse systems and circuits.

Performance Metrics Deciphered

Here, we embark on a journey to decode the performance metrics that delineate the component’s capabilities. From signal-to-noise ratio to frequency response, each metric holds significance in determining the component’s efficacy in specific applications.

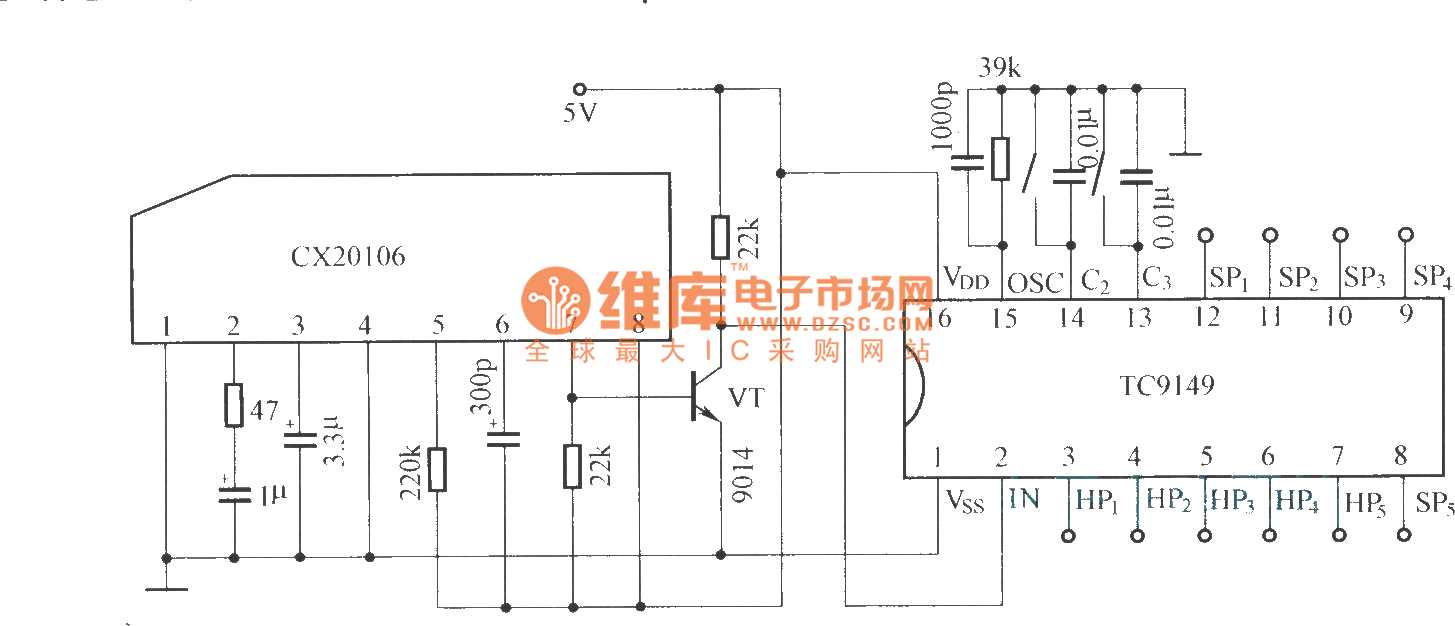

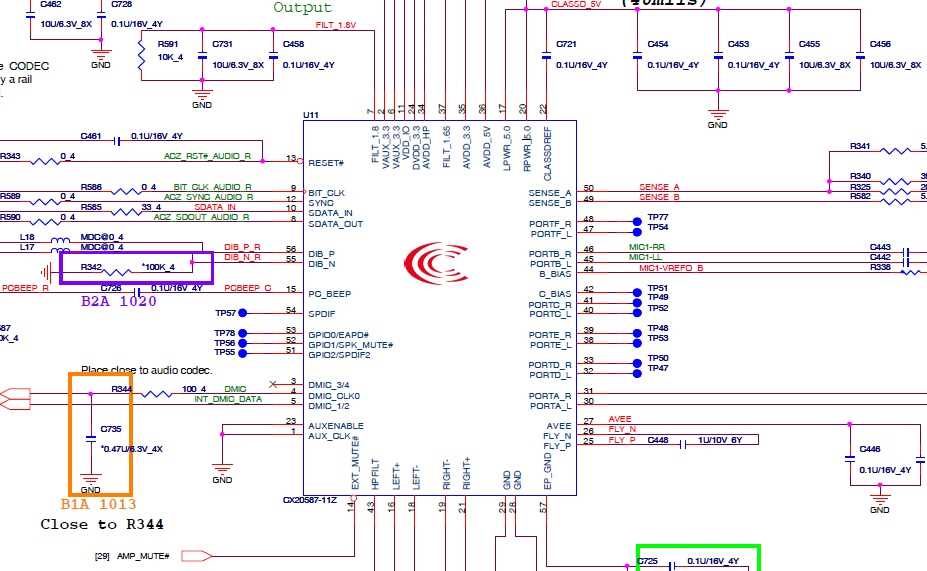

Pin Configuration and Functionality

In this section, we delve into the arrangement and operational roles of the pins pertinent to the component under scrutiny. Understanding the pin configuration and functionality is crucial for comprehending the interplay of signals and functionalities within the system. Each pin serves a distinct purpose, contributing to the overall performance and functionality of the device. Let’s explore the layout and roles of these pins in detail.

Optimizing Performance with CX20561 Documentation

In this section, we delve into strategies for enhancing efficiency and effectiveness through comprehensive utilization of the CX20561 technical specifications. By leveraging the wealth of information provided within this documentation, users can streamline operations, fine-tune functionality, and elevate overall system performance.

Understanding the Inner Workings

Before delving into optimization techniques, it’s imperative to grasp the intricacies and nuances encapsulated within the CX20561 documentation. By gaining insight into the underlying mechanisms and functionalities, users can discern potential areas for improvement and tailor strategies accordingly.

Maximizing Component Synergy

One key avenue for optimization lies in harnessing the synergistic potential of the CX20561 specifications with complementary components and peripherals. Through meticulous integration and alignment, users can unlock heightened levels of performance and functionality, thereby maximizing the value proposition of the entire system.

Fine-Tuning Parameters

Within the expansive landscape of the CX20561 documentation, users will encounter a plethora of parameters and configurations that directly influence performance outcomes. By strategically fine-tuning these variables in accordance with specific requirements and objectives, users can achieve optimal system performance tailored to their unique needs.

Implementing Best Practices

As users navigate the wealth of information provided within the CX20561 documentation, adherence to established best practices emerges as a guiding principle for optimization endeavors. By adhering to proven methodologies and industry standards, users can mitigate risks, enhance reliability, and expedite the optimization process.

Continuous Refinement and Iteration

Optimization is an iterative journey characterized by continuous refinement and enhancement. By treating the CX20561 documentation as a dynamic resource rather than a static reference, users can perpetually iterate upon their optimization strategies, ensuring sustained performance gains and adaptability to evolving requirements.

Best Practices for Implementation

When integrating the specifications and functionalities of the Cx20561 chipset into your project, adhering to industry best practices is paramount for seamless execution and optimal performance. This section outlines key guidelines and strategies for effectively incorporating the features of this component into your system.

- Thorough Component Analysis: Before embarking on the implementation process, conduct a comprehensive analysis of the chipset’s features, capabilities, and compatibility with your project requirements. Understanding the intricacies of the chipset will facilitate informed decision-making throughout the integration process.

- Clear Design Objectives: Define clear and concise design objectives that align with the overarching goals of your project. Establishing specific targets and performance metrics will guide the implementation process and enable you to gauge the success of your integration efforts.

- Modular Approach: Adopt a modular approach to implementation, breaking down the integration process into manageable components or modules. This approach promotes scalability, ease of maintenance, and facilitates iterative development, allowing for incremental improvements and optimizations.

- Robust Testing Regimen: Implement a rigorous testing regimen to validate the functionality, interoperability, and reliability of the integrated solution. Utilize both simulated environments and real-world scenarios to identify and rectify any potential issues or discrepancies before deployment.

- Documentation and Knowledge Sharing: Maintain detailed documentation throughout the implementation process, documenting design decisions, configurations, and any customizations made to the chipset. Foster a culture of knowledge sharing within your team, ensuring that insights and learnings are disseminated effectively.

- Compliance and Standards Adherence: Ensure compliance with relevant industry standards and regulatory requirements during the implementation process. Adhering to established protocols and guidelines mitigates the risk of compatibility issues and ensures interoperability with other system components.

By following these best practices, you can streamline the implementation of the chipset, maximize its potential, and achieve optimal performance within your project ecosystem.