Unlocking the heart of contemporary microcontrollers delves into the intricacies of their fundamental architecture and functionality. These miniature marvels power an array of modern devices, from automotive systems to industrial machinery, orchestrating complex operations with precision and efficiency.

Embark on a journey through the inner workings of these technological powerhouses as we navigate through the labyrinth of their capabilities and intricacies. Peel back the layers to reveal the intricate circuits, algorithms, and interfaces that define their operational essence.

Discover the pulsating core that drives innovation and empowers a myriad of applications, shaping the landscape of digital technology. Unravel the mysteries encoded within silicon, where every transistor, register, and instruction plays a vital role in orchestrating a symphony of computation.

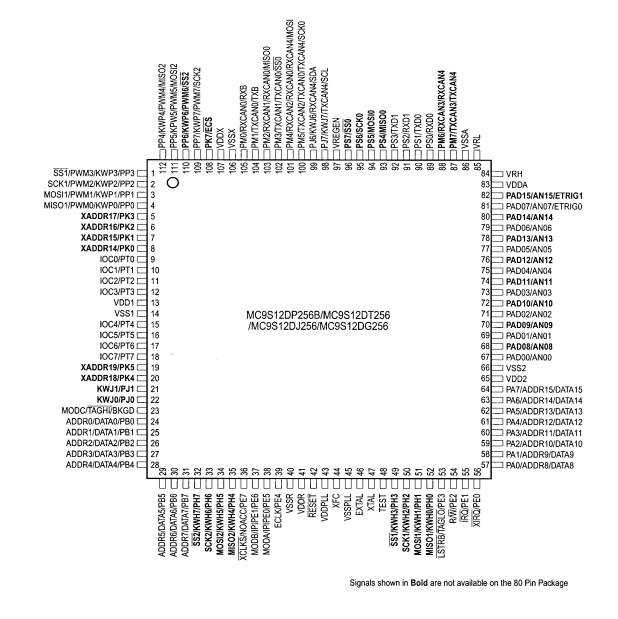

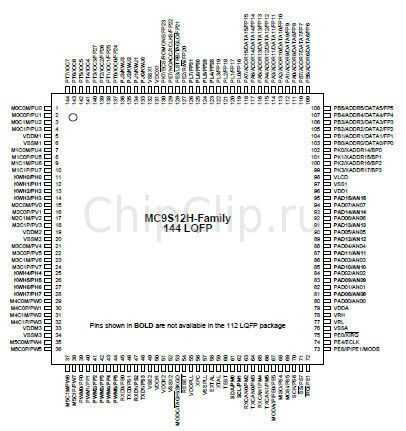

Unlocking the Potential: Exploring the Features of the Revolutionary S12 Microcontroller

Delve into the intricacies of this cutting-edge microcontroller as we uncover its myriad capabilities and functionalities. This section serves as a comprehensive guide to understanding the vast array of features embedded within this powerful device.

The Core Architecture

At the heart of this innovative microcontroller lies a sophisticated architecture engineered to deliver unparalleled performance and efficiency. Explore the intricate design that drives the seamless operation of the S12, empowering developers with unparalleled control and flexibility.

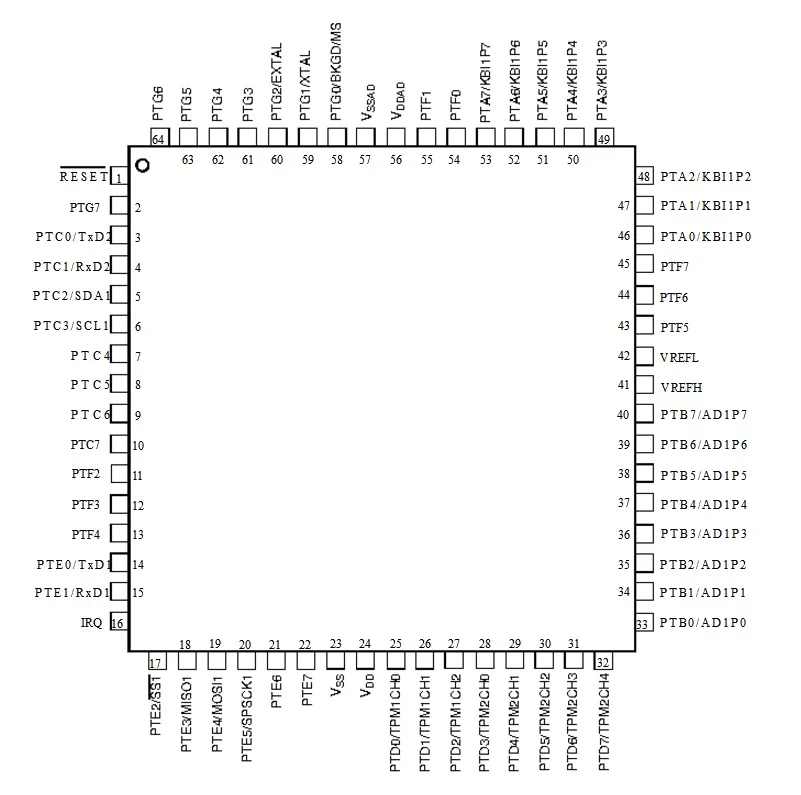

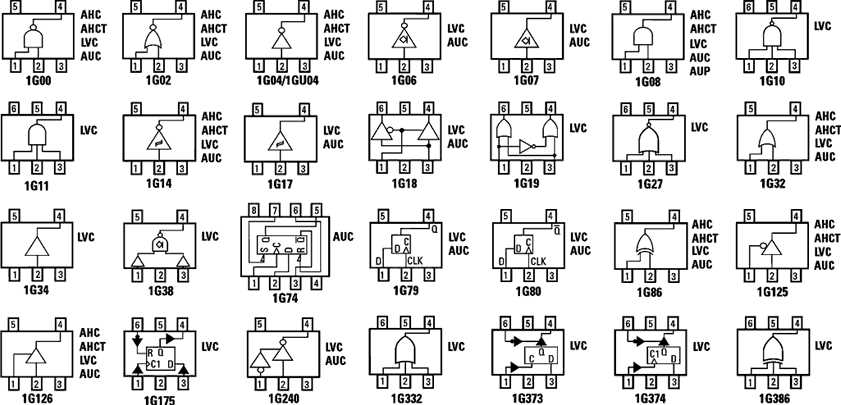

Peripheral Integration and Functionality

Unlock the full potential of your projects with the extensive range of integrated peripherals offered by the S12 microcontroller. From advanced timers and communication modules to versatile analog interfaces, explore how these features elevate your applications to new heights of sophistication and functionality.

| Feature | Description |

|---|---|

| Enhanced Timer Modules | Experience precise timing control and synchronization with the S12’s advanced timer modules, enabling seamless integration of time-sensitive operations into your applications. |

| Flexible Communication Interfaces | Facilitate seamless data exchange and communication between various system components using the S12’s versatile communication interfaces, including UART, SPI, and I2C protocols. |

| Analog-to-Digital Conversion | Harness the power of accurate analog-to-digital conversion capabilities to capture and process real-world signals with precision, ensuring optimal performance in a wide range of sensing and measurement applications. |

Demystifying the Core Architecture

In this section, we embark on a journey to unravel the intricate design of the central processing unit (CPU) within the microcontroller, shedding light on its fundamental structure and functionality. Delving into the heart of the microcontroller’s brain, we uncover the underlying principles governing its operation, dissecting its core architecture with a keen eye for detail.

Exploring the Essence: We delve into the essence of the CPU’s architecture, dissecting its intricate layers and functions. By peeling back the layers of complexity, we aim to elucidate the underlying principles that govern its operation, providing clarity amidst the technical jargon.

Anatomy of the Core: We embark on a journey through the anatomy of the CPU, exploring its various components and their interconnections. From the arithmetic logic unit (ALU) to the control unit, each element plays a crucial role in executing instructions and processing data.

Functionality Unveiled: Unveiling the functionality of the CPU, we examine how it interprets instructions, executes operations, and manages data flow. Through a comprehensive analysis, we aim to demystify the intricate processes underlying its operation, providing insights into its inner workings.

Optimization Strategies: We explore optimization strategies employed within the core architecture, focusing on enhancing performance, efficiency, and reliability. From instruction pipelining to memory management, we delve into techniques aimed at maximizing the microcontroller’s capabilities.

Conclusion: In concluding this exploration, we reflect on the insights gained into the core architecture of the microcontroller. By demystifying its inner workings, we empower readers to navigate the complexities of microcontroller design with confidence and clarity.

Navigating Peripheral Integration for Enhanced Functionality

Exploring the seamless amalgamation of hardware components to augment operational capabilities entails a meticulous understanding of peripheral integration dynamics. This section delves into the strategic orchestration of auxiliary modules to amplify system performance and versatility.

Optimizing Performance with Memory Management Strategies

In the realm of enhancing system efficiency and responsiveness, adept memory management plays a pivotal role. This section delves into a spectrum of strategies aimed at maximizing performance through astute handling of memory resources. By meticulously orchestrating memory utilization, systems can achieve heightened efficiency and responsiveness, ensuring seamless operation across various applications.

| Strategy | Description |

|---|---|

| Memory Allocation Optimization | Efficient allocation of memory resources to minimize fragmentation and maximize availability for critical operations. |

| Caching Mechanisms | Implementing caching mechanisms to expedite data retrieval and reduce latency, thereby enhancing overall system performance. |

| Memory Pooling | Pooling memory segments to facilitate swift allocation and deallocation, curtailing overhead associated with frequent memory requests. |

| Dynamic Memory Management | Utilizing dynamic memory allocation techniques to optimize memory usage dynamically based on runtime demands, fostering adaptive resource allocation. |

| Memory Compression | Implementing compression algorithms to minimize memory footprint without compromising data integrity, enabling efficient utilization of memory resources. |

| Memory Fragmentation Mitigation | Employing strategies to mitigate memory fragmentation, such as defragmentation routines or memory compaction, to ensure continuous availability of contiguous memory blocks. |

By leveraging these diverse strategies, systems can harness the full potential of memory resources, optimizing performance across a myriad of applications and use cases. The judicious implementation of memory management techniques empowers systems to navigate complex computational tasks with agility and efficiency, laying the foundation for robust and responsive operation.