In the labyrinth of electronic schematics lies a realm where bits and bytes find solace, where the dance of electrons orchestrates the symphony of data. At the heart of this digital symposium reside intricate memory modules, silently weaving the fabric of computational prowess. Today, we embark on a journey into the microcosm of silicon landscapes, delving into the essence of a quintessential component, known for its prowess in retaining transient thoughts and transient states.

In the realm of integrated circuits, where every nanometer counts, lies a chamber where memories are not merely stored, but crafted with precision akin to that of a master artisan. Within this domain, dwell devices that hold the whispers of binary code, preserving the essence of computational musings in fleeting electrical charges. These enigmatic constructs, revered as Random Access Memory (RAM), serve as the ephemeral custodians of digital intellect.

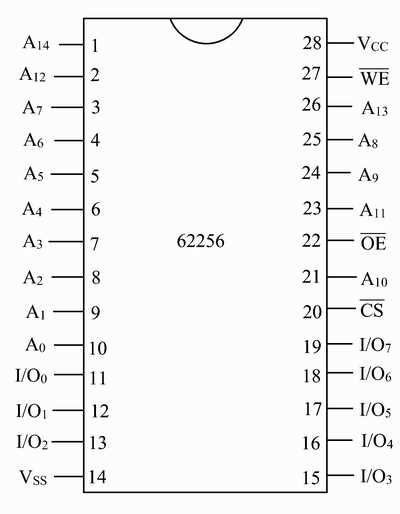

As we navigate through the corridors of technological intrigue, we encounter a particular incarnation of RAM, a stalwart guardian known by the cryptic code 62256. This sentinel, obscured behind the veil of alphanumeric nomenclature, stands as a testament to the ingenuity of silicon craft. Within its confines, a symphony of transistors orchestrates a ballet of data, performing the delicate balance between access speed and storage capacity with unparalleled finesse.

Understanding the Operational Dynamics of 62256 Static Random-Access Memory

In this section, we delve into the intricate workings of a specific type of memory technology, shedding light on its operational mechanisms and applications. Through a detailed exploration, we aim to provide a comprehensive understanding of the operational dynamics inherent to the 62256 SRAM module.

The Essence of Static RAM

Static Random-Access Memory, abbreviated as SRAM, constitutes a pivotal component within modern computing systems. Unlike its counterpart, Dynamic RAM (DRAM), SRAM maintains data without the need for periodic refreshing, ensuring rapid access times and low latency. This inherent characteristic of SRAM renders it indispensable in various computing applications where speed and efficiency are paramount.

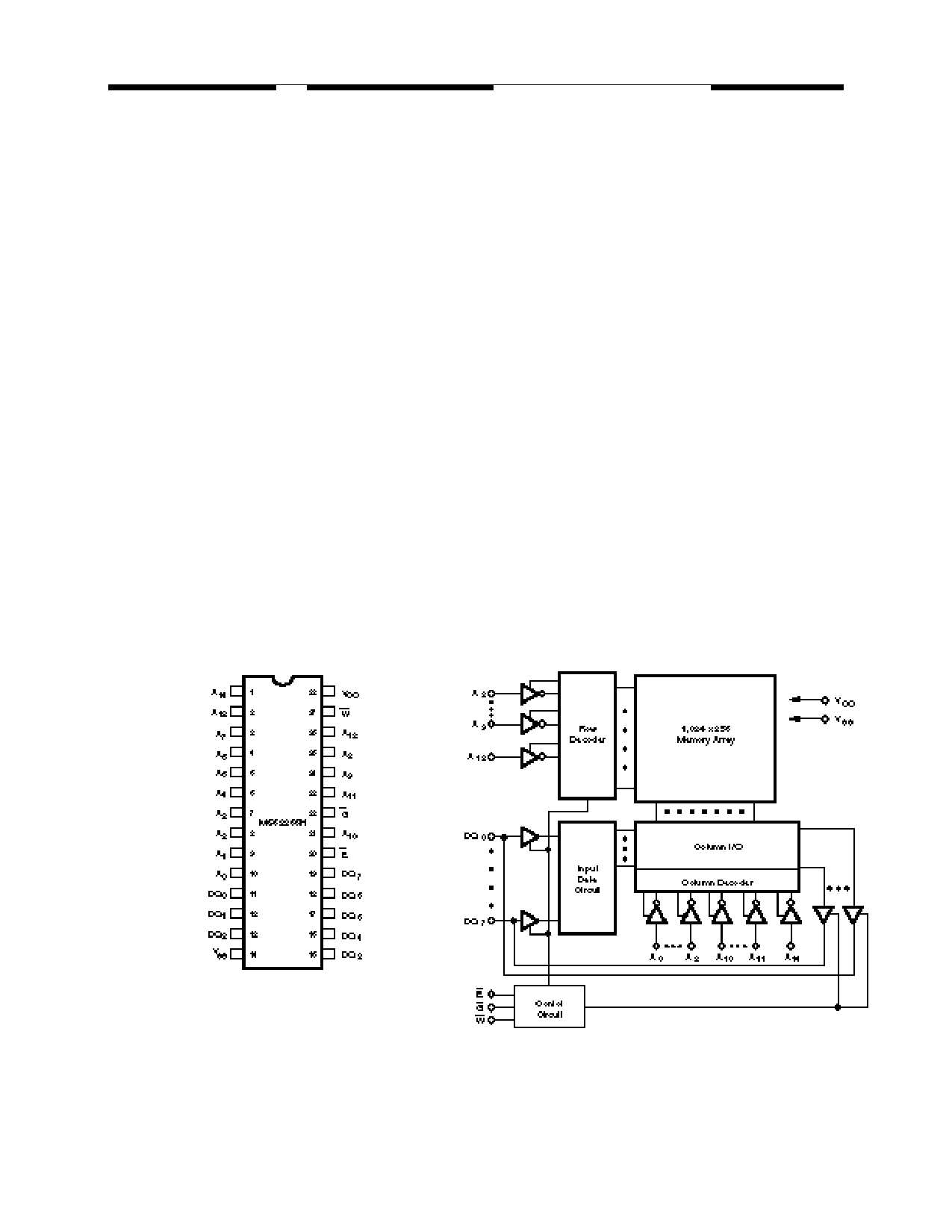

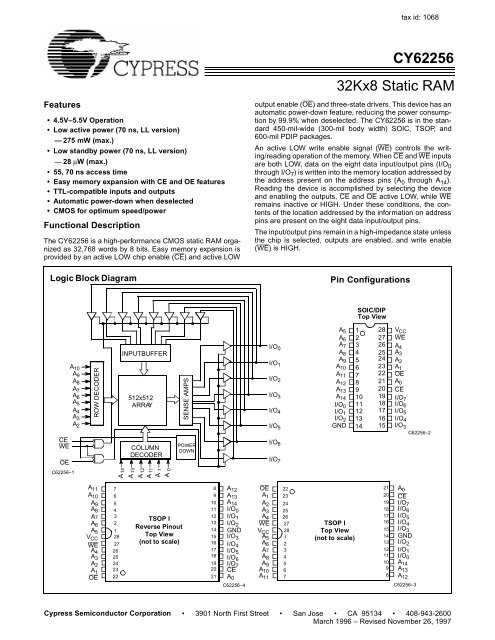

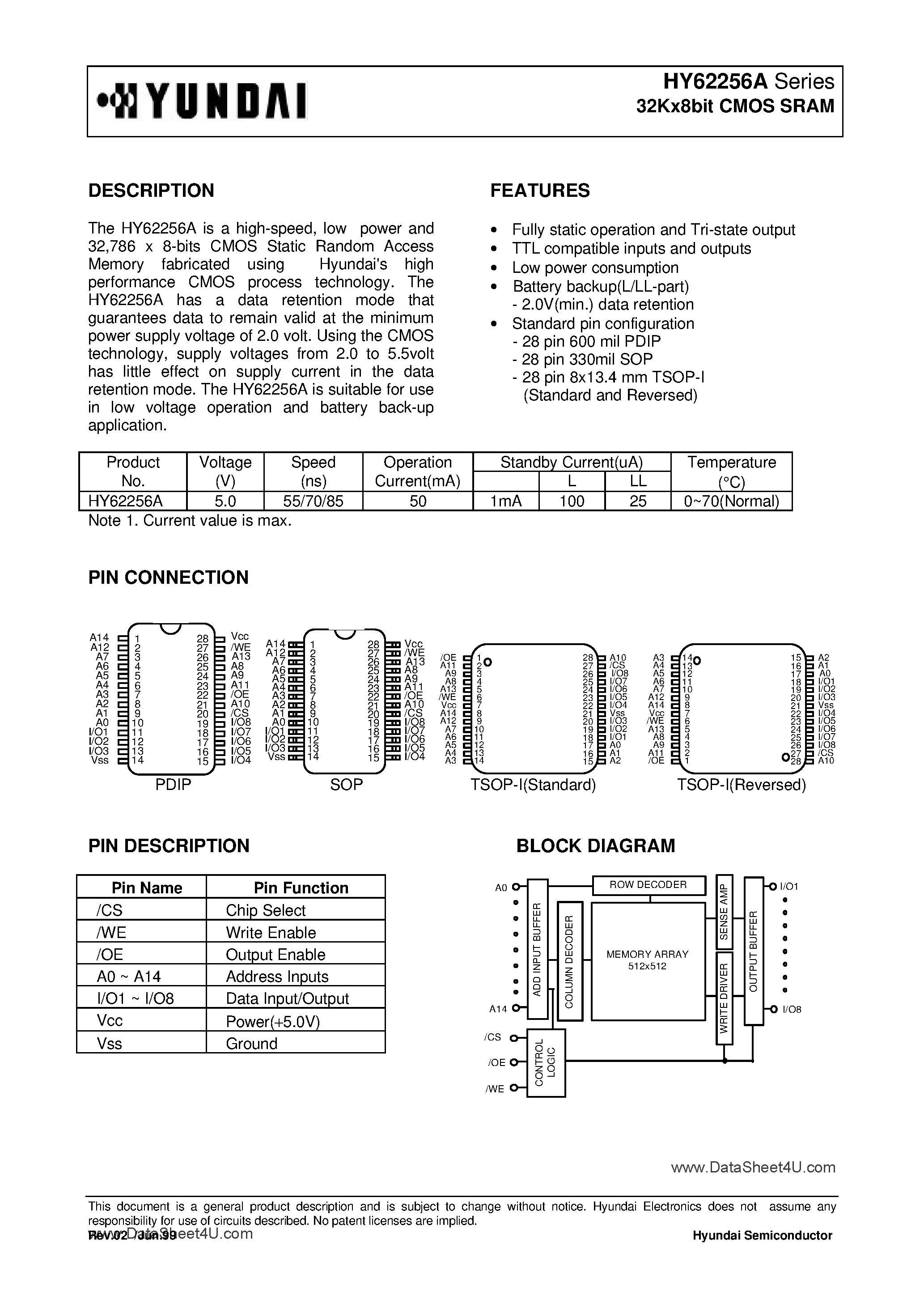

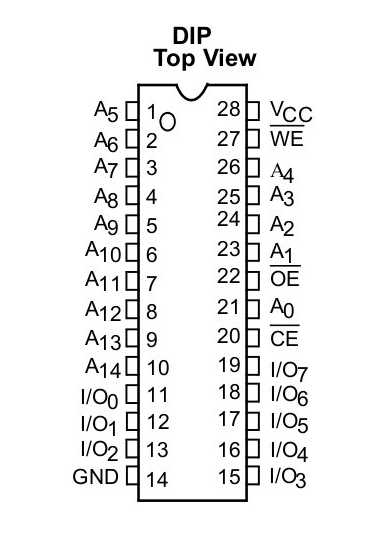

Functional Architecture and Operational Principles

At the core of the 62256 SRAM module lies a sophisticated architecture designed to facilitate swift data access and retrieval. Through a combination of flip-flops and associated circuitry, SRAM accomplishes the storage and manipulation of binary data with remarkable efficiency. By elucidating the operational principles underpinning this architecture, we aim to demystify the inner workings of the 62256 SRAM, unraveling its functionality in the process.

- Exploration of Cell Structure and Data Storage Mechanisms

- Analysis of Read and Write Operations: Addressing and Timing Considerations

- Understanding Power Consumption and Standby Modes

- Insights into Data Retention and Stability

Through an in-depth examination of these facets, we endeavor to equip readers with a profound understanding of the functionality of 62256 SRAM, elucidating its role as a cornerstone of contemporary computing architectures.

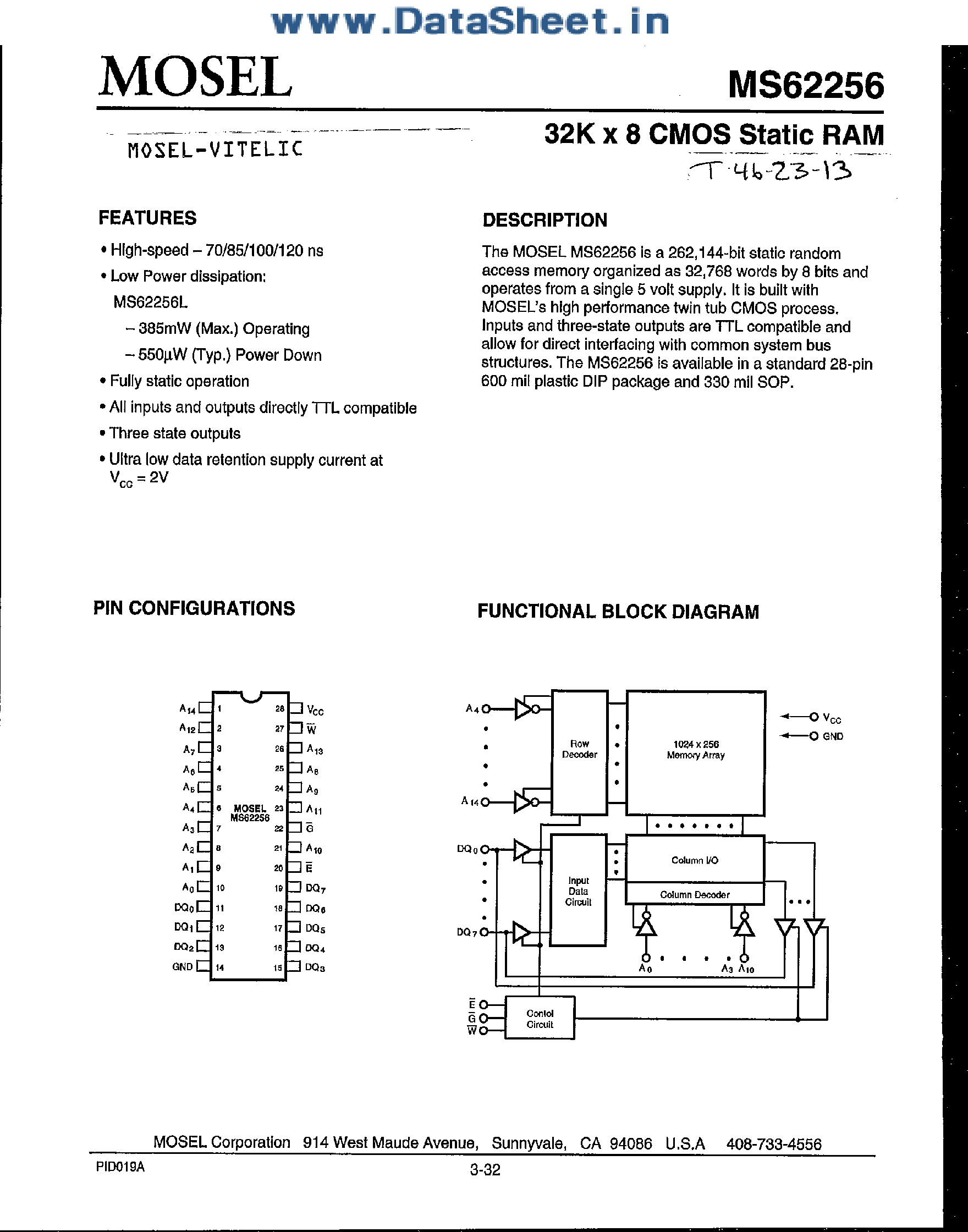

Exploring the Technical Specifications and Features

In this section, we delve into the intricate details and distinctive attributes of the SRAM module, shedding light on its comprehensive technical specifications and rich array of features. We embark on a journey to unravel the intricacies of this dynamic component, unveiling its underlying capabilities and functionalities.

We commence our exploration by dissecting the technical specifications, unraveling the intricate framework that governs the performance and functionality of this memory module. From speed and access times to capacity and voltage requirements, each aspect contributes to the holistic understanding of its operational prowess.

Furthermore, we navigate through the diverse features embedded within this SRAM module, elucidating its versatility and adaptability across various applications. From advanced data retention mechanisms to robust error-correction protocols, each feature enhances its efficacy in demanding scenarios.

As we delve deeper into the realm of technical intricacies, we uncover the nuances that define the SRAM module’s functionality, offering insights into its operational parameters and performance benchmarks. Through meticulous examination, we unravel the underlying mechanisms that propel this component to unparalleled heights of efficiency and reliability.

By the culmination of this exploration, we aspire to equip readers with a comprehensive understanding of the technical specifications and features encapsulated within this SRAM module, empowering them to harness its full potential in diverse technological endeavors.

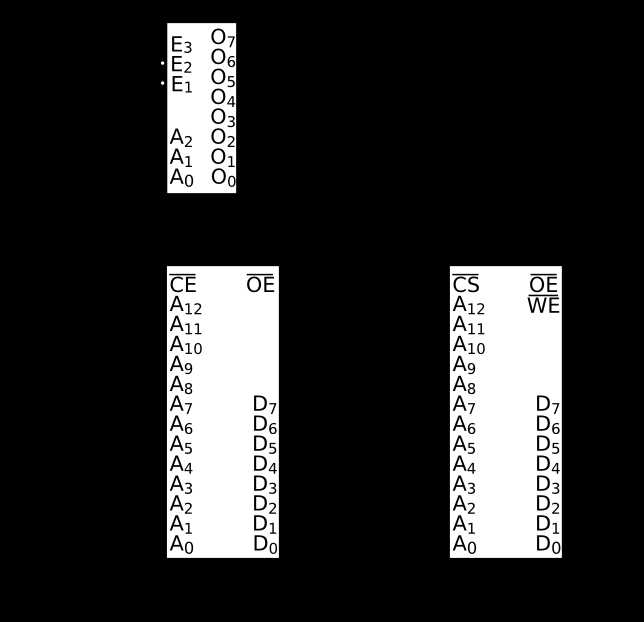

Practical Applications and Integration Considerations

Exploring the real-world applications and seamless integration strategies of this high-speed static random-access memory (SRAM) component unveils a spectrum of possibilities for its utilization across diverse technological landscapes. Understanding the nuanced ways in which this robust memory module can be integrated into various systems not only enhances performance but also optimizes efficiency.

Optimizing System Performance

Efficiently harnessing the capabilities of this advanced memory unit can significantly elevate system performance across multiple domains. By strategically incorporating it into the architecture, developers can streamline data processing, minimize latency, and bolster overall operational speed. Whether employed in embedded systems, IoT devices, or high-performance computing clusters, the judicious integration of SRAM ensures seamless functionality and heightened responsiveness.

Integration Challenges and Solutions

While the benefits of integrating SRAM into diverse applications are evident, navigating the associated integration challenges is paramount. Addressing issues such as power consumption, signal integrity, and compatibility with existing hardware requires meticulous planning and innovative solutions. Through thorough system analysis and strategic design modifications, engineers can overcome these hurdles and unlock the full potential of SRAM integration, ushering in a new era of efficiency and performance.

Tips for Enhancing SRAM Efficiency and Resolving Issues

In this section, we’ll explore strategies to optimize the performance and troubleshoot common challenges encountered when working with static random-access memory (SRAM). By implementing these techniques, you can maximize the utilization of SRAM resources and address potential issues effectively.

1. Efficient Utilization Strategies

- Implementing Data Compression Techniques: Reduce the amount of data stored in SRAM by employing compression algorithms, thereby optimizing memory utilization without compromising performance.

- Utilizing Data Caching Mechanisms: Implement caching strategies to store frequently accessed data in SRAM, enhancing overall system performance by reducing access latency to critical information.

- Optimizing Memory Access Patterns: Analyze and optimize memory access patterns to minimize contention and maximize throughput, ensuring efficient utilization of SRAM resources.

2. Troubleshooting Techniques

- Addressing Write Noise Issues: Identify and mitigate potential write noise problems by adjusting voltage levels, implementing error correction codes (ECC), or employing specialized circuitry to maintain data integrity in SRAM cells.

- Resolving Timing Violations: Detect and resolve timing violations by analyzing signal integrity, adjusting clock frequencies, or optimizing routing paths to ensure reliable data transmission and access within the SRAM module.

- Debugging Address Line Interference: Investigate and resolve address line interference issues by isolating signal pathways, enhancing shielding techniques, or implementing error detection mechanisms to prevent data corruption in SRAM addresses.

By incorporating these tips for efficient utilization and troubleshooting techniques, you can enhance the performance and reliability of SRAM-based systems, ensuring optimal operation in various applications.